# MULTI-INNO TECHNOLOGY CO., LTD.

# **LCD MODULE SPECIFICATION**

Model : MI4004D

| Revision      |  |

|---------------|--|

| Engineering   |  |

| Date          |  |

| Our Reference |  |

# CONTENTS

| NO | ITEM                                                  | PAGE |

|----|-------------------------------------------------------|------|

| 1  | COVER                                                 | 1    |

| 2  | CONTENTS                                              | 2    |

| 3  | PRECAUTIONS FOR LCM                                   | 3    |

| 4  | OPTICAL DEFINITIONS                                   | 5    |

| 5  | TIMING CHARACTERISTICS AND ELECTRICAL CHARACTERISTICS | 6    |

| 6  | FUNCTION DESCRIPTION                                  | 8    |

| 7  | INSTRUCTION DESCRIPTION                               | 13   |

| 8  | QUALITY AND RELIABILITY                               | 20   |

| 9  | OUTLINE DIMENSION                                     | 22   |

| 10 | OPERATING OPTION                                      | 23   |

|    |                                                       |      |

|    |                                                       |      |

## 3. PRECAUTIONS FOR LCM

## 3.1 Precautions in handling LCD Modules (hereinafter LCMs)

Multi-Inno's LCMs have been assembled and accurately calibrated before delivery.

Please observe the following criteria when handling.

- A. Do not subject the module to excessive shock.

- B. Do not modify the tab on the metal holder.

- C. Do not tamper with the printed circuit board.

- D. Limit the soldering of the printed circuit board to I/O terminals only.

- E. Do not touch the zebra strip nor modify its location.

#### 3.2 Static electricity warning

Multi-Inno's LCM uses CMOS LSI technology. Therefore, strict measures to avoid static electricity discharge are followed through all processes from manufacturing to shipping. When handling a LCM, take sufficient care to prevent static electricity discharge as you would any CMOS IC.

A. Do not take the LCM from its anti-static bag until it's to be assembled.

LCM's are individually packaged in bags specially treated to resist static electricity. When storing, keep the LCM packed in the original bags, or store them in a container processed to be resistant to static electricity, or in an electric conductive container.

B. Always use a ground strap when handling a LCM.

Always use a ground strap while working with the module, from the time it is taken out of the anti-static bag until it is assembled. If it is necessary to transfer the LCM, once it has been taken out of the bag, always place it in an electric conductive container. Avoid wearing clothes made of chemical fibers, the use of cotton or conductive treated fiber clothing is recommended.

C. Use a no-leak iron for soldering the LCM.

The soldering iron to be used for soldering the I/O terminals to the LCM are to be insulated or grounded at the iron tip.

D. Always ground electrical apparatuses required for assembly.

Electrical apparatuses required to assemble the LCM into a product, i.e. electrical screw drivers, are to be first grounded to avoid transmitting spike noises from the motor.

E.Assure that the work bench is properly grounded.

F. Peel off the LCM protective film slowly.

The module is attached with a film to protect the display surface from contamination, damage, adhesion of flux, etc. Peeling off this film abruptly could cause static electricity to be generated, so peel the tape slowly.

G. Pay attention to the humidity in the work area.

50~60% RH is recommended.

#### 3.3 Precautions for the soldering of a LCM

The following procedures should be followed when soldering the LCM:

- A. Solder only to the I/O terminal.

- B. Use a no leakage soldering iron and pay particular attention to the following:

- (1) Conditions for soldering I/O terminals

Temperature at iron tip:  $280^{\circ}$ C +  $10^{\circ}$ C

Soldering time: 3~4 sec/terminal

Type of solder: Eutectic solder (rosin flux filled)

Note: (Avoid using flux, because it could penetrate the module and the module may get contaminated during cleaning.) Peel off protective film after soldering the I/O terminals. By following this procedure, the surface contamination caused by the dispersion of flux while soldering can be avoided.

(2) Removing the wiring

(When a lead wire, or a connector to the I/O terminal of the module is to be removed, remove it only after the solder at the connection has sufficiently melted since the I/O terminal is a through hole.) If it is forcefully removed, it could cause the terminal to break or peel. The recommended procedure is to use a suction-type solder remover. Caution: do not reheat the I/O terminal more than 3 times.

#### 3.4 Long-term storage

If the correct method of storage is not followed, deterioration of the display material (polarizer) and oxidation of the I/O terminal plating may make the process of soldering difficult. Please comply with the following procedure.

A. Store in the shipping container.

- B. If the shipping container is not available, place in anti-static bags and seal the opening.

- C. Store the modules where they are not subjected to direct sunlight or a fluorescent lamp.

D. Store in a temperature range of  $0^{\circ}$ C - 35  $^{\circ}$ C with low relative humidity.

MULTI-INNO TECHNOLOGY CO,. LTD

MI4004D

#### 3.5 Precautions in use of LCD modules

- A. Do not give any external shock.

- B. Do not wipe the surface with hard materials.

- C. Do not apply excessive force on the surface.

- D. Do not expose to direct sunlight or fluorescent light for a long time.

- E. Avoid storage in high temperature and high humidity.

- F. When storage for a long time at  $40^{\circ}$ C or higher is required, R/H should be less than 60%.

- G. Liquid in LCD is hazardous substance. Do not lick, swallow when the liquid is attached to your hands, skin, clothes etc. Wash it out thoroughly.

#### **4. OPTICAL DEFINITIONS**

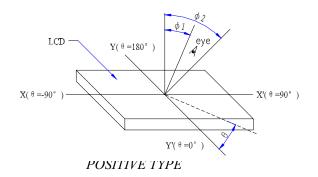

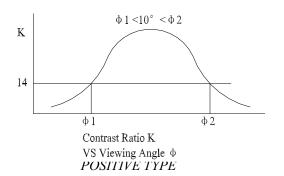

#### **4.1 Definition of angle** $\theta$ and $\phi$

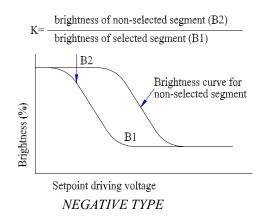

#### 4.3 Definition of contrast "K"

#### 4.5 Definition of contrast "K"

###

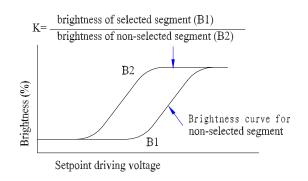

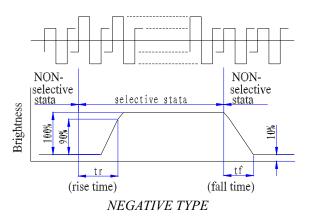

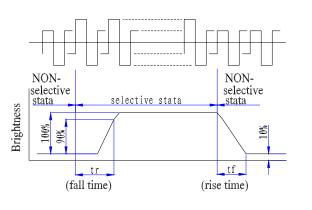

#### 4.4 Definition of optical response

#### 4.6 Definition of optical response

MULTI-INNO TECHNOLOGY CO,. LTD

**MI4004D**

**PAGE:4/23**

# 5. Timing Characteristics and Electrical Characteristics

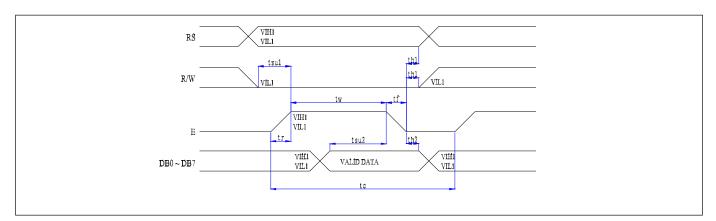

# **5.1 Timing Characteristics**

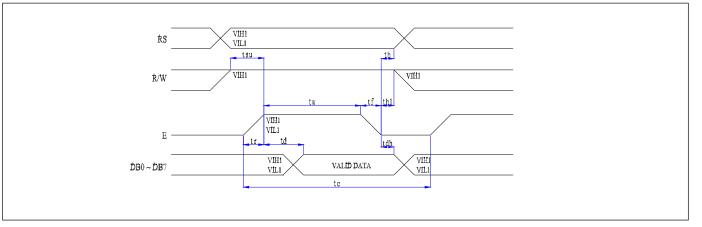

|                     | (VDD=4.5V to 5.5          | V, Ta=-30 to    | +85 ℃ |      |     | )    |

|---------------------|---------------------------|-----------------|-------|------|-----|------|

| Mode                | Item                      | Symbol          | Min   | Туре | Max | Unit |

|                     | E Cycle Time              | ts              | 500   |      |     | ns   |

|                     | E Rise / Fall Time        | tr, tf          |       |      | 20  | ns   |

|                     | E Pulse Width (High, Low) | tw              | 230   |      |     | ns   |

| Write Mode          | R/W and RS Setup Time     | tsu1            | 40    |      |     | ns   |

| (Refer to Figure 1) | R/W and RS Hold Time      | th1             | 10    |      |     | ns   |

|                     | Data Setup Time           | tsu2            | 80    |      |     | ns   |

|                     | Data Hold Time            | th2             | 10    |      |     | ns   |

|                     | E Cycle Time              | tc              | 500   |      |     | ns   |

|                     | E Rise / Fall Time        | tr,tf           |       |      | 20  | ns   |

|                     | E Pulse Width (High, Low) | tw              | 230   |      |     | ns   |

| Read mode           | R/W and RS Setup Time     | tsu             | 40    |      |     | ns   |

| (refer to figure 2) | R/W and RS Hold Time      | th              | 10    |      |     | ns   |

|                     | Data Output Time          | t <sub>D</sub>  |       |      | 120 | ns   |

|                     | Data Hold Time            | t <sub>DH</sub> | 5     |      |     | ns   |

|                     | (VDD=2.7V to 4.5          | V, Ta=-30 to -  | +85 ℃ |      |     | )    |

|---------------------|---------------------------|-----------------|-------|------|-----|------|

| Mode                | Item                      | Symbol          | Min   | Туре | Max | Unit |

|                     | E Cycle Time              | tc              | 1000  |      |     | ns   |

|                     | E Rise / Fall Time        | tr, tf          |       | 25   | ns  |      |

| W. t. M. J.         | E Pulse Width (High, Low) | tw              | 450   |      |     | ns   |

| Write Mode          | R/W and RS Setup Time     | tsu1            | 60    |      |     | ns   |

| (Refer to Figure 1) | R/W and RS Hold Time      | th1             | 20    |      |     | ns   |

|                     | Data Setup Time           | tsu2            | 195   |      |     | ns   |

|                     | Data Hold Time            | th2             | 10    |      |     | ns   |

|                     | E Cycle Time              | tc              | 1000  |      |     | ns   |

|                     | E Rise / Fall Time        | tr,tf           |       |      | 25  | ns   |

|                     | E Pulse Width (High, Low) | tw              | 450   |      |     | ns   |

| Read mode           | R/W and RS Setup Time     | tsu             | 60    |      |     | ns   |

| (refer to figure 2) | R/W and RS Hold Time      | th              | 20    |      |     | ns   |

|                     | Data Output Time          | t <sub>D</sub>  |       |      | 360 | ns   |

|                     | Data Hold Time            | t <sub>DH</sub> | 5     |      |     | ns   |

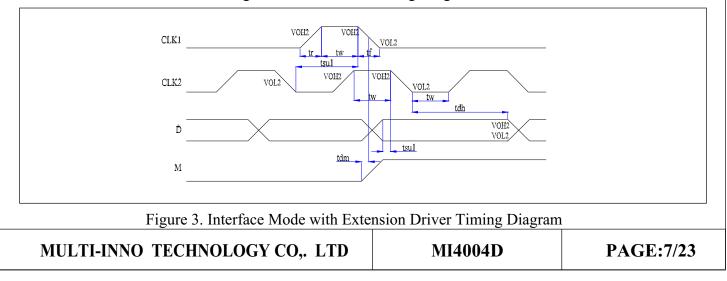

| Mode                                                              | Item                          | Symbol          | Min   | Туре | Max  | Unit |

|-------------------------------------------------------------------|-------------------------------|-----------------|-------|------|------|------|

|                                                                   | Clock Pulse Width (High, Low) | tw              | 800   |      |      | ns   |

|                                                                   | Clock Rise/Fall Time          | tr, tf          |       |      | 25   | ns   |

| Interface Mode<br>with Extension<br>Driver (refer to<br>figure 3) | Clock Setup Time              | tsu1            | 500   |      |      | ns   |

|                                                                   | Data Setup Time               | tsu2            | 300   |      |      | ns   |

|                                                                   | Data Hold Time                | t <sub>D</sub>  | 300   |      |      | ns   |

|                                                                   | M Delay Time                  | t <sub>DH</sub> | -1000 |      | 1000 | ns   |

# Figure 1. Write Mode Timing Diagram

Figure 2. Read Mode Timing Diagram

# **5.2 Electrical Characteristics**

| PARAMETER                       | SYMBOL        | CONDITION    | MIN. | ТҮР | MAX. | UNIT |  |  |  |  |  |  |

|---------------------------------|---------------|--------------|------|-----|------|------|--|--|--|--|--|--|

| H LEVEL INPUT VOLTAGE           | VIH           |              | 2.2  |     |      | V    |  |  |  |  |  |  |

| L LEVEL INPUT VOLTAGE           | VIL           |              |      |     | 0.6  | V    |  |  |  |  |  |  |

| H LEVEL OUTPUT VOLTAGE          | VOH           | -IOH=0.205mA | 2.4  |     |      | V    |  |  |  |  |  |  |

| L LEVEL OUTPUT VOLTAGE          | VOL           | IOL=1.2mA    |      |     | 0.4  | V    |  |  |  |  |  |  |

| POWER SUPPLY CURRENT<br>(LOGIC) | IDD           | VDD=5.0V     |      | 1.0 | 3    | mA   |  |  |  |  |  |  |

| RECOMMENDED                     | VDD-V0        | Ta=0 ℃       |      | 4.6 |      | V    |  |  |  |  |  |  |

| LCD DRIVING                     | DUTY=1/16     | Ta=25 ℃      |      | 4.2 |      | V    |  |  |  |  |  |  |

| VOLTAGE                         | $\Phi=25^{0}$ | Ta=50°C      |      | 3.8 |      | V    |  |  |  |  |  |  |

| CLOCKOSCILLATION<br>FREQUENCY   | FOSC          | Ta=25 ℃      |      | 270 |      | KHz  |  |  |  |  |  |  |

DC Characteristics(VDD=4.5V to 5.5V, Ta=-30 to +85°C)

# **6 FUNCTION DESCRIPTION**

### 6.1 System Interfac e

This chip has all two kinds of interface type with MPU: 4-bit bus and 8-bit bus is selected by DL bit in the instruction register. During read or write operation, two 8-bit registers are used. One is data register (DR), the other is instruction register (IR). The data register (DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM. The target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. So to speak, after MPU reads DR data, the data in the next DDRAM/CGRAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM automatically. The instruction register(IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data. To select register, use RS input pin in 4-bit /8-bit bus mode.

# Table 1. Various Kinds of Operations according to RS and R/W Bits

| RS | R/W | Operation                                                         |

|----|-----|-------------------------------------------------------------------|

| L  | L   | Instruction Write operation (MPU writes instruction code into IR) |

| L  | Н   | Read Busy flag (DB7) and address counter (DB0~DB6)                |

| Н  | L   | Data Write operation (MPU writes data into DR)                    |

| Н  | Н   | Data Read operation (MPU reads data from DR)                      |

# 6.2 Busy Flag (BF)

When BF=High, it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS=Low and R/W=High (Read instruction Operation), through DB7 port. Befroe executing the next instruction, be sure that BF is not High..

| <b>MULTI-INNO TECI</b> | HNOLOGY CO | LTD |

|------------------------|------------|-----|

|------------------------|------------|-----|

MI4004D

# 6.3 Address Counter (AC)

Address Counter(AC) stores DDRAM/CGRAM address, transferred from IR. After writing into (reading from) DDRAM/CGRAM, AC is automatically increased (decreased) by 1. When RS=Low and R/W=High, AC can be read through DB0 – DB6 ports.

# 6.4 Display Data RAM (DDRAM)

DDRAM stores display data of maximum 80 x 8 bits (80 characters). DDRAM address is set in the

address counter (AC) as a hexadecimal number. (refer to Fig-4 )

| MSB |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|

| AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Figure 4. DDRAM Address

# 1) 1-line Display

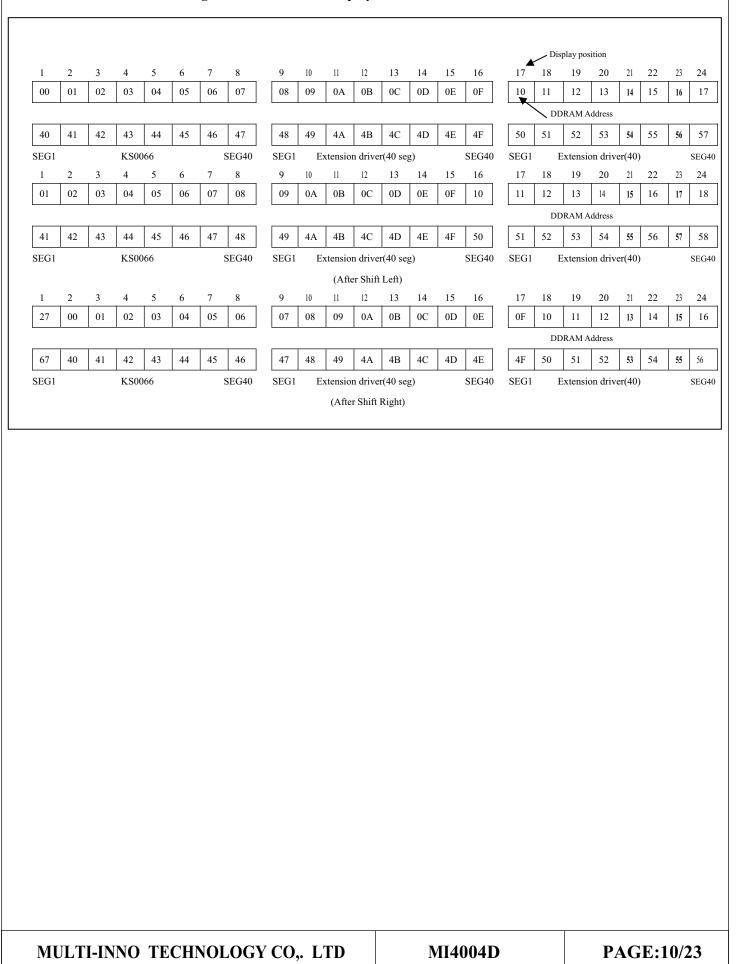

In the case of a 1-line display, the address range of DDRAM is 00H-04H. An Extension driver will be used. Figure 5 shows the example when a 40-segment extension driver is added.

Display position COM1 0A 0B 0C0D0E 0F COM8 KS0066 SEG40 SEG1 SEG40 SEG1 Extension driver(40 seg) SEG1 Extension driver(40) SEG40 DDRAM Address COM1 0A 0B 0C 0D0E 0F COM8 SEG1 KS0066 SEG40 SEG1 Extension driver(40 seg) SEG40 SEG1 Extension driver(40) SEG40 (After Shift Left) COM1 4F 0A 0B0C 0D 0E0F COM8 SEG40 SEG1 Extension driver(40 seg) SEG40 SEG1 KS0066 SEG1 Extension driver(40) SEG40 (After Shift Right)

Figure 5. 1-line x 24ch. Display with 40 SEG. Extension Driver

# 2) 2-line Display

In the case of a 2-line display, the address range of DDRAM is 00H-27H and 40H-67H.An Extension driver will be used. Figure 6 shows the example a 40-segment extension Driver is added.

MULTI-INNO TECHNOLOGY CO,, LTD

Figure 6. 2-line x 24ch. Display with 40 SEG Extension Driver

# 6.5 Character generator ROM (CG ROM)

|      | LLLL             | LLHL              | LLHH                   | LHLL   | LHLH                                                                                      | LHHL                                                       | СННН                                               | HLLL | HLLH | HLHL                                               | HLHH                                             | HHLL                                                                                                   | HHLH                                                                                          | HHHL                                        | нннн                                                                                       |

|------|------------------|-------------------|------------------------|--------|-------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------|------|------|----------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------|

| LLLL | CG<br>RAM<br>(1) |                   |                        | 9      |                                                                                           | <b>.</b>                                                   |                                                    |      |      |                                                    | a 2 0 8 8                                        |                                                                                                        | 82 5<br>92 9<br>93 9<br>9                                                                     | Ċ.                                          |                                                                                            |

| LLLH | (2)              | 8                 |                        |        |                                                                                           | 888<br>9220<br>9 <mark>829</mark><br>9225                  | -                                                  |      |      | 89 8<br>8 9<br>88 8                                |                                                  |                                                                                                        |                                                                                               | 0 8<br>92 8<br>2 92<br>2 92<br>2 92<br>2 92 |                                                                                            |

| LLHL | (3)              |                   |                        |        |                                                                                           |                                                            |                                                    |      |      | 8<br>8<br>9 8 90                                   | 4                                                | ų,                                                                                                     | ×                                                                                             |                                             |                                                                                            |

| LLHH | (4)              |                   |                        |        | ;<br>                                                                                     |                                                            | 9 <mark>889</mark><br>8889<br>8889                 |      |      |                                                    |                                                  |                                                                                                        | 8 09 09<br>8 99 89<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | • • • •<br>• • • •                          |                                                                                            |

| LHLL | (5)              |                   |                        | D      | 8 8 8 8<br>8<br>8<br>8<br>9<br>8<br>9<br>8<br>9                                           |                                                            | <b>t</b>                                           |      |      | Α.                                                 |                                                  |                                                                                                        |                                                                                               |                                             |                                                                                            |

| LHLH | (6)              | •                 |                        |        |                                                                                           | 809<br>80985<br>80985<br>8099                              | ÷;                                                 |      |      | 88                                                 |                                                  | 20200<br>20200<br>2020<br>2020<br>2020                                                                 | 89 5<br>9<br>9<br>9 99 99<br>9 99 99                                                          |                                             |                                                                                            |

| СННГ | (7)              |                   |                        |        | I.,I                                                                                      |                                                            | i.,i                                               |      |      |                                                    |                                                  | 825                                                                                                    | 2 22 29<br>5 22 29<br>6 22 29<br>6 22 89                                                      |                                             | 00000<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 |

| СННН | (8)              | 2                 | 7                      |        | ļ,                                                                                        | 8 2 2 2<br>2 5<br>2 9 2 5<br>2 9 2 5<br>2 9 2 5<br>2 9 2 5 | Ļ,                                                 |      |      |                                                    | 2 2 2 2 2<br>2 2 2 2 2<br>2 2 2 2 2<br>2 2 2 2 2 | •••••                                                                                                  |                                                                                               |                                             |                                                                                            |

| HLLL | (1)              | <                 | 8                      |        | X                                                                                         |                                                            | ×                                                  |      |      | 4                                                  |                                                  |                                                                                                        |                                                                                               | .,                                          | <br>X                                                                                      |

| HLLH | (2)              | $\langle \rangle$ |                        |        | <b>.</b> ,1                                                                               |                                                            | 8 8<br>8 8<br>8 8<br>8 8<br>8 8                    |      |      |                                                    |                                                  |                                                                                                        |                                                                                               | 1                                           | 9 9<br>9 9<br>9 9<br>9 9<br>9 9<br>9 9<br>9 9                                              |

| HLHL | (3)              | : <b>:</b> ::     |                        |        | 2000<br>2<br>2<br>2<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                                                            | 01020<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |      |      |                                                    |                                                  | Ĥ                                                                                                      |                                                                                               |                                             |                                                                                            |

| нгнн | (4)              |                   | **                     | К      |                                                                                           |                                                            | <                                                  |      |      | 83 5 2 8<br>8 8<br>9 8<br>9 8<br>9 8               | •                                                | 2<br>2 03 29<br>2<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9 |                                                                                               | ×                                           |                                                                                            |

| HHLL | (5)              |                   | <                      | !<br>! |                                                                                           |                                                            |                                                    |      |      |                                                    |                                                  | 22 22<br>9<br>9                                                                                        | 2 22 22<br>2 2<br>9                                                                           | :                                           |                                                                                            |

| ннгн | (6)              | 82928             | 5 5 5 5 5<br>5 5 5 5 5 |        |                                                                                           |                                                            | >                                                  |      |      |                                                    |                                                  | ^                                                                                                      | •••<br>••••                                                                                   |                                             | 8<br>8 88 8 8<br>9                                                                         |

| нннс | (7)              |                   | $\geq$                 |        | .**.                                                                                      |                                                            | a 20 a                                             |      |      | 85 8 9<br>9<br>8 8 8 9<br>8 8 8<br>8 8<br>8 8<br>8 |                                                  |                                                                                                        | •••                                                                                           |                                             |                                                                                            |

| нннн | (8)              |                   | ?                      | 0      | 0 00 00                                                                                   |                                                            |                                                    |      |      |                                                    | 1.<br>                                           | 20000<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2             | 9 09<br>9 0<br>9 20<br>9 20                                                                   |                                             |                                                                                            |

# The relationship between character codes and Character Patterns

MULTI-INNO TECHNOLOGY CO,, LTD

# 6.6 CGROM (Character Generator ROM)

CGROM has a 5 x 8 dots 204 characters pattern and a 5 x 10 dots 32 characters pattern. CGROM has 204 character patterns of 5 x 8 dots, and 32 character patterns of 5 x 11 dots.

# 6.7 CGRAM (Character Generator RAM)

CGRAM has up to 5 x 8 dot, 8 characters. By writing font data to CGRAM, user defined characters can be used (Refer to table 1).

| Character Code (DDRAM data) |     |     |     |     |     | M da | ıta) | (   | CGR | AM  | [ Ad | dres | S  |    |    | CG  | RA | ΜI  | Data | l   |    | Pattern |

|-----------------------------|-----|-----|-----|-----|-----|------|------|-----|-----|-----|------|------|----|----|----|-----|----|-----|------|-----|----|---------|

| D7                          | D 6 | D 5 | D 4 | D 3 | D 2 | D 1  | D 0  | A 5 | A4  | A 3 | A2   | A 1  | A0 | Р7 | P6 | P 5 | P4 | P3  | P 2  | P 1 | P0 | number  |

| 0                           | 0   | 0   | 0   | x   | 0   | 0    | 0    | 0   | 0   | 0   | 0    | 0    | 0  | x  | x  | x   | 0  | 1   | 1    | 1   | 0  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 0    | 0    | 1  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 0    | 1    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     | •   |     |      |      |     |     |     | 0    | 1    | 1  |    |    |     | 1  | 1   | 1    | 1   | 1  |         |

|                             |     |     |     | •   |     |      |      |     | •   |     | 1    | 0    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     | •   |     |      |      |     |     |     | 1    | 0    | 1  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 1    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 1    | 1  |    |    |     | 0  | 0   | 0    | 0   | 0  |         |

|                             |     |     |     | •   |     |      |      |     |     |     | •    |      |    |    |    |     |    | •   |      |     |    |         |

|                             |     |     |     | •   |     |      |      |     |     |     | •    |      |    |    |    |     |    | •   |      |     |    |         |

| 0                           | 0   | 0   | 0   | х   | 1   | 1    | 1    | 0   | 0   | 0   | . 0  | 0    | 0  | x  | x  | x   | 1  | . 0 | 0    | 0   | 1  | •       |

| 0                           | 0   | 0   | 0   | л   | 1   | 1    | 1    | 0   | 0   | 0   | 0    | 0    | 1  | л  | л  | л   | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 0    | 1    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 0    | 1    | 1  |    |    |     | 1  | 1   | 1    | 1   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 0    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 0    | 1  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 1    | 0  |    |    |     | 1  | 0   | 0    | 0   | 1  |         |

|                             |     |     |     |     |     |      |      |     |     |     | 1    | 1    | 1  |    |    |     | 0  | 0   | 0    | 0   | 0  |         |

| Table 1. Relationship Between Character Code (DDRAM) and Character Patter | tern (CGROM) |

|---------------------------------------------------------------------------|--------------|

|---------------------------------------------------------------------------|--------------|

" $\overline{x}$ " Don't care

#### 6.8 Timing Generation Circuit

Timing generation circuit generates clock signals for the internal operations.

#### 6.9 LCD Driver Circuit

LCD Driver circuit has 16 common and 40 segment signals for LCD driving. Data from CGRAM/CGROM is transferred to 40 bit segment latch serially, and then it is stored to 40 bit shift latch. When each common is selected by 16 bit common register, segment data also output through

MULTI-INNO TECHNOLOGY CO,. LTD

segment driver from 40 bit segment latch, In case of 1-line display mnode, COM1-COM8 have 1/8 duty or COM1-COM11 have 1/11 duty, and in 2-line mode, COM1 – COM16 have 1/16 duty ratio.

# 6.10 Cursor/Blink Control Circuit

It controls cursor/blink ON/OFF at cursor position.

# **7 INSTRUCTION DESCRIPTION**

# 7.1 Outline

To overcome the speed difference between internal clock of KS0066 and MPU clock, KS0066 performs internal operation by storing control information to IR or DR. The internal operation is determined according to the signal from MPU, composed of read/write and data bus. (refer to Table 3) Instruction can be divided largely four kinds.

1) KS0066 function set instructions (set display methods, set data length, etc.)

- 2) Address set instructions to internal RAM.

- 3) Data transfer instructions with internal RAM.

- 4) Others.

The address of internal RAM is automatically increased or decreased by 1.

NOTE: During internal operation, Busy Flag (DB7) is read "High". Busy Flag check must precede the next instruction. When an MPU program with checking the Busy Flag (DB7) is made, it must be necessary 1/2 fosc for executing the next instruction by the falling edge of the 'E' signal after the Busy Flag (DB7) goes to "Low".

# Contents

# 1) Clear Display

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter). Return cursor to the original status, namely, bring the cursor to the left edge on first line of the display. Make entry mode increment (I/D ="1"). 2) **Return Home**

| ] | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |     |

eturn Home is cursor return home instruction. Set DDRAM address to "00H" in the address cousor. Return cursor to its original site and return display to its original status, if shifted. Contents of DDRAM does not change

| MULTI-INNO TECHNOLOGY CO,. LTD | MI4004D | PAGE:13/23 |

|--------------------------------|---------|------------|

|--------------------------------|---------|------------|

# 3) Entry Mode Set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | SH  |

Set the moving direction of cursor and display.

### I/D: Increment / decrement of DDRAM address (cursor or blink)

When I/D = "High", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D = "Low", cursor/blink moves to left and DDRAM address is decreased by 1.

\* CGRAM operates the same as DDRAM, when reading from or write to CGRAM.

### SH: Shift of Entire Display

When DDRAM read (CGRAM read/write) operation or SH = "Low", shift of entire display is not performed. If SH = "High" and DDRAM write operation, shift of entire display is performed according to I/D value (I/D= "1": shift left, I/D="0": shift right)

### 4) Display ON/OFF Control

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | C   | В   |

Control display/cursor/blink ON/OFF 1 bit register.

# **D: Display ON/OFF Control Bit**

When D= "High", entire display is turned on.

When D= "Low", display is turned off, but display data is remained in DDRAM.

# C: Cursor ON/OFF Control Bit

When C= "High", cursor is turned on.

When C= "Low", cursor is disappeared in current display, but I/D register remains its data.

#### **B:** Cursor Blink ON/OFF Control Bit

When B= "High", cursor blink is on, that performs alternate between all the high data and display

character at the cursor position. When B= "Low", blink is off.

# 5) Display ON/OFF Control

RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

MULTI-INNO TECHNOLOGY CO,. LTD

| 0 | 0 | 0 | 0 | 0 | 1 | S/C | R/L |  |  |

|---|---|---|---|---|---|-----|-----|--|--|

|---|---|---|---|---|---|-----|-----|--|--|

Shifting of right/left cursor position or display without writing or reading of display data. This instruction is used to correct or search display data (Refer to table 2). During 2-line mode display, cursor moves to the 2nd line after the 40th digit of the 1st line. Note that display shift is performed simultaneously in all the lines. When displayed data is shifted repeatedly, each line is shifted individually. When display shift is performed, the contents of the address counter are not changed.

#### Table 2. Shift Patterns According to S/C and R/L Bits

| S/C | R/L | Operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, AC is decreased by 1                            |

| 0   | 1   | Shift cursor to the right, AC is increased by 1                           |

| 1   | 0   | Shift all the display to the left, cursor moves according to the display  |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

### 6) Function Set

| <br>RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0      | 0   | 0   | 0   | 1   | DL  | Ν   | F   |     |     |

## **DL: Interface Data Length Control Bit**

When DL= "High", it means 8-bit bus mode with MPU.

When DL= "Low", it means 4-bit bus mode with MPU. So to speak, DL is a signal to select 8-bit or 4-bit bus mode.

When 4-bit bus mode, it needs to transfer 4-bit data by two times.

#### N: Display line number control bit

When N= "Low", it means 1-line display mode.

When N= "High", 2-line display mode is set.

#### F: Display Font Type Control Bit

When F= "Low", 5 x 7 dots format display mode.

When F= "High", 5 x 10 dots format display mode.

# 7) Set CGRAM Address

| . = |   |   |   |     | DB4 |     |     |     |     |

|-----|---|---|---|-----|-----|-----|-----|-----|-----|

| 0   | 0 | 0 | 1 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

MULTI-INNO TECHNOLOGY CO,. LTD MI4004D PAGE:15/23

Set CGRAM address to AC. This instruction makes CGRAM data available from MPU.

#### 8) Set DDRAM Address

|   |   |   |     |     | DB4 |     |     |     |     |

|---|---|---|-----|-----|-----|-----|-----|-----|-----|

| 0 | 0 | 1 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC. This instruction makes DDRAM data available from MPU. When 1-line display mode (N=0), DDRAM address is from "00H" to "4FH". In 2-line display mode (N=1), DDRAM address in the 1st line is from "00H" to "27H", and DDRAM address in the 2nd line is from "40H" to "67H".

#### 9) Read Busy Flag & Address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

This instruction shows whether KS0066 is in internal operation or not. If the resultant BF is High, it means the internal operation is in progress and you have to wait until BF to be Low, and then the next instruction can be performed. In this instruction you can read also the value of address counter. **10) Write Data to RAM**

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM. The selection of RAM from DDRAM, CGRAM, is set by the previous address set instruction: DDRAM address set. RAM set instruction can also determine the AC direction to RAM. After write operation, the address is automatically increased/decreased by 1, according to the entry mode.

#### 11) Read Data from RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM. The selection of RAM is set by the previous address set instruction. If the address set instruction of RAM is not performed before this instruction, the data that read first is invalid, because the direction of AC is not determined. If you read RAM data several times without RAM address set instruction before read operation, you can get correct RAM data from the second, but the first data would be incorrect, because there is no time margin to

MULTI-INNO TECHNOLOGY CO,. LTD

transfer RAM data. In case of DDRAM read operation, cursor shift instruction plays the same role

as DDRAM address set instruction; it also transfer RAM data to output data register. After read

operation, address counter is automatically increased/decreased by 1 according to the entry mode.

After CGRAM read operation, display shift may not be executed correctly.

**NOTE**: In case of RAM write operation, after this AC is increased/decreased by 1 like read operation. In this time, AC indicates the next address position, but you can read only the previous data by read instruction.

| Instruction                      | DC | D/N | DD5 |     | truct |     |     | DDA | DD1 | DDO | Description<br>instruction code                                                                                                          | Execution<br>time<br>(fosc=270kHz) |

|----------------------------------|----|-----|-----|-----|-------|-----|-----|-----|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|                                  | RS | R/W | DB7 | DB6 | DB5   | DB4 | DB3 | DB2 | DB1 | DB0 |                                                                                                                                          |                                    |

| Clear display                    | 0  | 0   | 0   | 0   | 0     | 0   | 0   | 0   | 0   | 1   | Write "20H" to DDRAM, and<br>set DDRAM address to "00H"<br>from AC.                                                                      | 1.53ms                             |

| Return home                      | 0  | 0   | 0   | 0   | 0     | 0   | 0   | 0   | 1   | X   | Set DDRAM address to "00H"<br>from AC and return cursor to<br>its original position if shifted                                           | 1.53ms                             |

| Entry mode set                   | 0  | 0   | 0   | 0   | 0     | 0   | 0   | 1   | I/D | SH  | Assign cursor moving<br>direction and make shift of<br>entire display                                                                    | 39us                               |

| Display<br>ON/OFF<br>control     | 0  | 0   | 0   | 0   | 0     | 0   | 1   | D   | С   | В   | Set display (D), cursor(C), and<br>blinking of cursor (B) on/off<br>control bit.                                                         | 39us                               |

| Cursor or<br>display shift       | 0  | 0   | 0   | 0   | 0     | 1   | S/C | R/L | X   | x   | Set cursor moving and display<br>shift control bit, and the<br>direction, without changing<br>DDRAM data.                                | 39us                               |

| Function set                     | 0  | 0   | 0   | 0   | 1     | DL  | N   | F   | X   | x   | Set interface data length (DL:<br>4-bit/8-bit), numbers of display<br>line (N: 1-line/2-line), display<br>font type (F:5x8dots/5x11dots) | 39us                               |

| Set CGRAM<br>address             | 0  | 0   | 0   | 1   | AC5   | AC4 | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address counter.                                                                                                    | 39us                               |

| Set DDRAM<br>address             | 0  | 0   | 1   | AC6 | AC5   | AC4 | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address counter.                                                                                                    | 39us                               |

| Read busy<br>flag and<br>address | 0  | 1   | BF  | AC6 | AC5   | AC4 | AC3 | AC2 | AC1 | AC0 | Whether during internal<br>operation or not can be known<br>by reading BF. The contents of<br>address counter can also be<br>read.       | Ous                                |

| Write data to<br>RAM             | 1  | 0   | D7  | D6  | D5    | D4  | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM).                                                                                              | 43us                               |

| Read data<br>from RAM            | 1  | 1   | D7  | D6  | D5    | D4  | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM).                                                                                               | 43us                               |

#### **Table 3. Instruction Table**

NOTE: When an MPU program with checking the Busy Flag (DB7) is made, it must be necessary 1/2 fosc is necessary for executing the next instruction by the falling edge of the 'E' signal after the Busy Flag (DB7) goes to "Low".

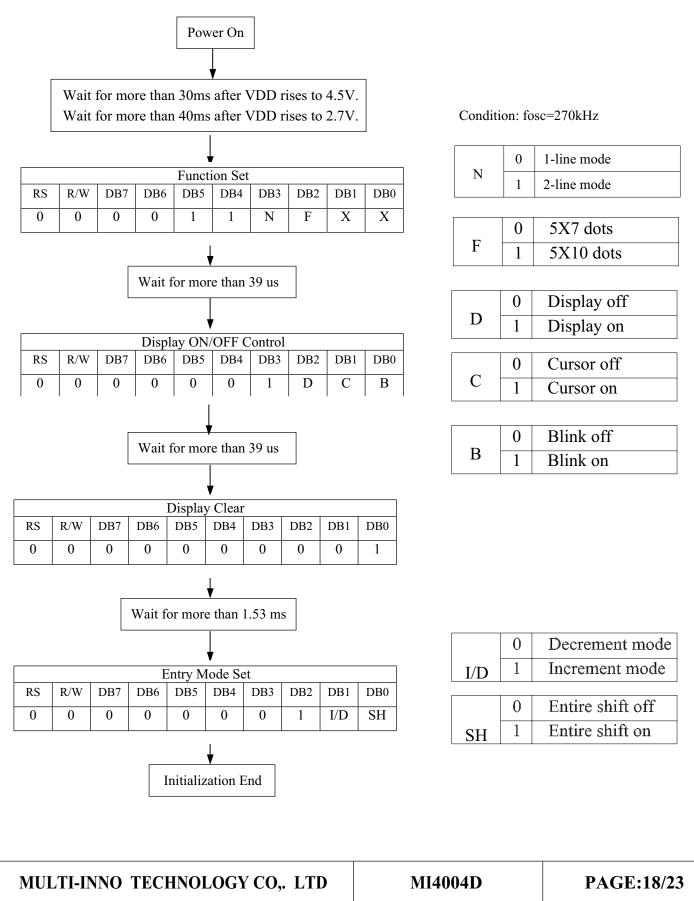

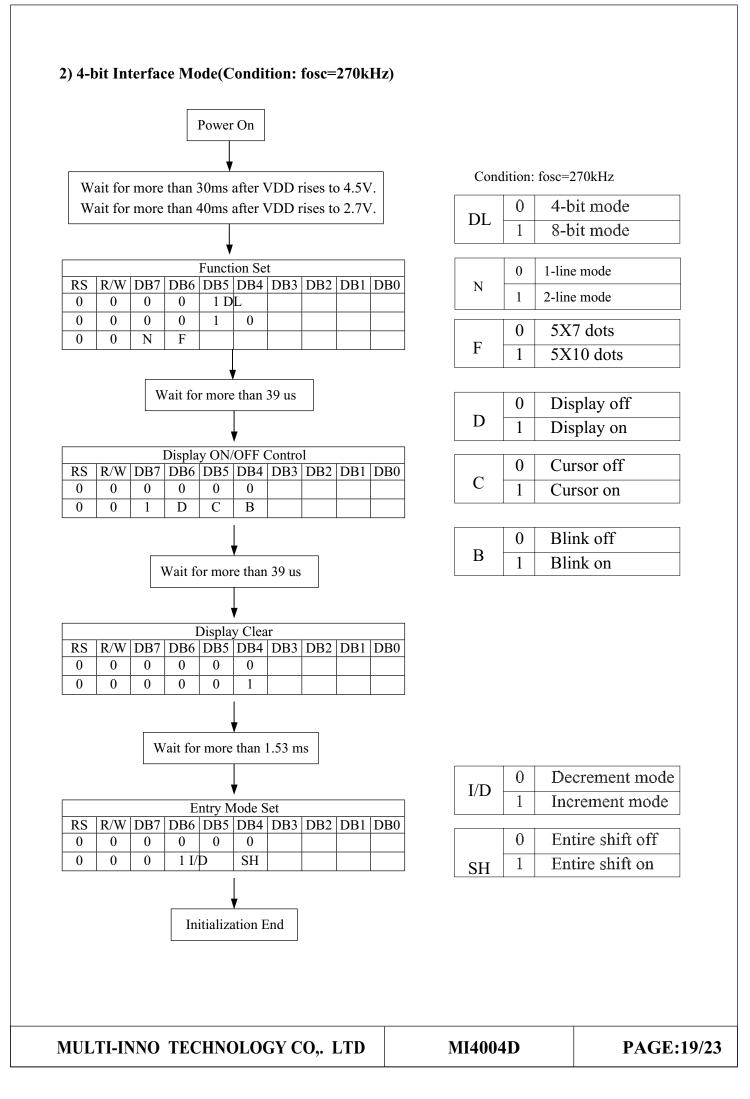

# 7.2 INITIALIZING BY INSTRUCTION

If the internal reset circuit doesn't operate correctly, initialization by instruction is required. Use the following procedure for initialization.

# 1) 8-bit Interface Mode(Condition: fosc=270kHz)

# **8 QUALITY AND RELIABILITY**

#### 8.1 Test condition

Test should be conducted under the following conditions:

Ambient temperature: 25  $\pm$  5 °C

Humidity :  $60 \pm 20\%$  RH

#### 8.2 Sampling plan

Sampling method shall be in accordance with MI4004D, inspection level II, normal inspection, and single sampling plan tables for normal tightened, and reduced inspection.

#### 8.3 Acceptable quality level

A major defect is a defect that could result in failure or materially reduce that the usability of the unit of product for its intended purpose.

A minor defect is one that does not materially reduce the usability of the unit of product for its intended purpose or is a departure from established standards having no significant bearing on the effective use or operation of the unit.

#### 8.4 Appearance

Appearance test is to be conducted by human eyes at approximately 30cm distance from LCD module under the single fluorescent light.

The inspection area of LCD panel shall be within the range. Of following limits.

# 8.5 Inspection quality criteria

| ITME                    | DESCRIPTION                                                                | Class of defects              | Acceptable<br>level (%) |       |     |  |  |  |

|-------------------------|----------------------------------------------------------------------------|-------------------------------|-------------------------|-------|-----|--|--|--|

| FUNCTION                | Short circuit or Pattern cut                                               | Major                         | 0.65                    |       |     |  |  |  |

| DIMENSION               | Refer to individual accepta                                                | nce specific                  | ation                   | Major | 2.5 |  |  |  |

|                         | Ave. Dia. D                                                                | area A                        | area B                  |       |     |  |  |  |

|                         | D 0.2                                                                      | Dis                           | sregard                 |       |     |  |  |  |

| BLACK SPOTS             | 0.2 <d 0.3<="" td=""><td>2</td><td>3</td><td>Minor</td><td>2.5</td></d>    | 2                             | 3                       | Minor | 2.5 |  |  |  |

|                         | 0.3 <d 0.4<="" td=""><td>0</td><td>1</td><td></td><td></td></d>            | 0                             | 1                       |       |     |  |  |  |

|                         | 0.4 <d< td=""><td colspan="6"></td></d<>                                   |                               |                         |       |     |  |  |  |

|                         | Width W, Length L                                                          | В                             |                         |       |     |  |  |  |

|                         | W 0.03                                                                     |                               |                         |       |     |  |  |  |

| BLACK LINES             | 0.03 <w 0.05<="" td=""><td>Minor</td><td>2.5</td></w>                      | Minor                         | 2.5                     |       |     |  |  |  |

|                         | 0.05 <w 0.07,="" 3.0<="" l="" td=""><td></td><td></td></w>                 |                               |                         |       |     |  |  |  |

| BUBBLES IN<br>POLARIZER | Average diameter D<br>0.2 < D < 0.5mm for N = -<br>0.5 < D < 0.7mm for N=1 | 4                             |                         | Minor | 2.5 |  |  |  |

| COLOR<br>UNIFORMITY     | Rainbow color or Newton                                                    | Rainbow color or Newton ring. |                         |       |     |  |  |  |

| GLASS<br>SCRATCHES      | Obvious visible damage.                                                    | Minor                         | 2.5                     |       |     |  |  |  |

| VIEWING ANGLE           | Refer to individual accept                                                 | Minor                         | 2.5                     |       |     |  |  |  |

| CONTRAST RATIO          | Refer to individual accept                                                 | cation                        | Minor                   | 2.5   |     |  |  |  |

| RESPONSE TIME           | Refer to individual accept                                                 | ance specifi                  | cation                  | Minor | 2.5 |  |  |  |

# 8.6 Reliability

The LCD module should have no failure in the following reliability test.

| TEST ITEM                  | TEST CONDITIONS                                                                     | NOTE |

|----------------------------|-------------------------------------------------------------------------------------|------|

| HIGH TEMPERATURE STORAGE   | 80°C , 200hr.                                                                       | Note |

| LOW TEMPERATURE STORAGE    | -30°C, 200hr                                                                        | Note |

| HUMIDITY STORAGE           | 60℃, 90%RH, 96hr.                                                                   | Note |

| HIGH TEMPERATURE OPERATION | 70°C, typical operating conditions, 200hr.                                          | Note |

| LOW TEMPERATURE OPERATION  | -20°C, typical operating conditions, 200hr.                                         | Note |

| TEMPERATURE CYCLING        | -30℃ ~ 80℃<br>10min, between each step temp.<br>50min, at each step temp. 5 cycles. | Note |

| MECHANICAL VIBRATION       | $10 \sim 100$ Hz sweep, 4G, amp1 = 10mm(max)<br>XYZ for 60min, each.                | Note |

| MECHANICAL SHOCK           | 10 ~ 55Hz, 50G.<br>XYZ for 1 time, each.                                            | Note |

NOTE 1: The module should not have condensation of water on the module.

NOTE 2: The module shelled be inspected after 1 hour storage in normal conditions (15~35°C 45~65%RH).

MULTI-INNO TECHNOLOGY CO,. LTD

**MI4004D**

# **Display Data Address**

| Character | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Line 1    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 20 | 21 | 22 | 23 |

| Line 2    | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 | 51 | 52 | 53 |

| Line 3    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 20 | 21 | 22 | 23 |

| Line 4    | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 | 51 | 52 | 53 |

| Character | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| Line 1    | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1D | 1E | 1F | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| Line 2    | 54 | 55 | 56 | 57 | 58 | 59 | 5A | 5B | 5C | 5D | 5E | 5F | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 |

| Line 3    | 14 | 15 | 16 | 17 | 18 | 19 | 1A | 1B | 1C | 1D | 1E | 1F | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| Line 4    | 54 | 55 | 56 | 57 | 58 | 59 | 5A | 5B | 5C | 5D | 5E | 5F | 60 | 61 | 62 | 63 | 64 | 65 | 66 | 67 |

#### **NOTES:**

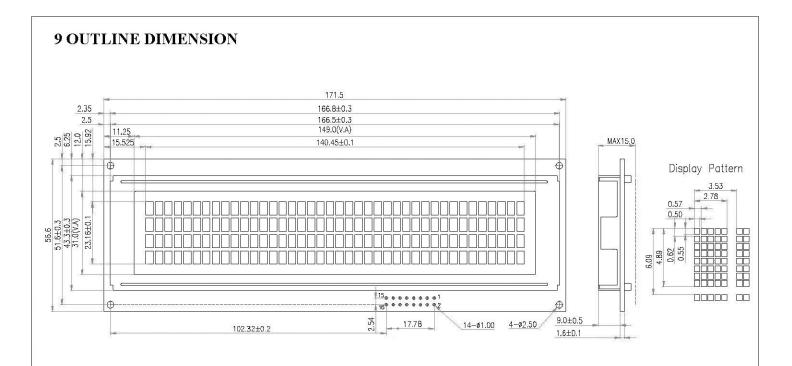

- 1. DISPLAY TYPE: STN Y-G, TRASFLECTIVE/POSITIVE.

- 2. DRIVE: KS0066U OR EQUIAL

- 3. VIEWING ANGLE: 6 O' CLOCK.

- 4. PIN CONNECTION:

| 1   | 2   | 3  | 4  | 5   | 6 | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15    | 16    |

|-----|-----|----|----|-----|---|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|

| VSS | VDD | VO | RS | R/W | Е | DB0 | DB1 | DB2 | DB3 | DB4 | DB5 | DB6 | DB7 | VLED+ | VLED- |

5. OPERATING TEMP: -20~70 .

**6.** STORAGE TEMP -30~80

7. BACKLIGHT : Y-G LIGHT BOTTOM.

8. RoHS

MULTI-INNO TECHNOLOGY CO., LTD

MI4004D

PAGE:22/23

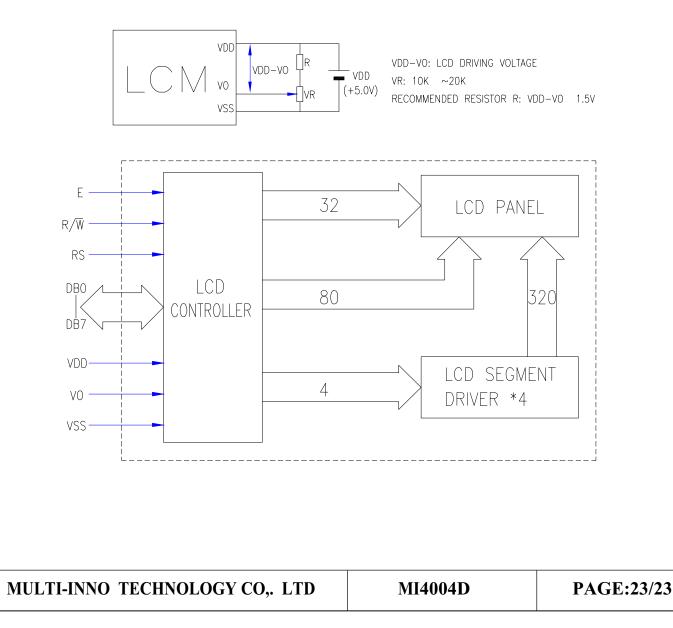

# **10. OPERATING OPTION**

# **10.1 Input signal Function**

| No.  | Symbol  | Function                         | Note |

|------|---------|----------------------------------|------|

| 1    | VSS     | Ground (0V)                      |      |

| 2    | VDD     | Power Suply for Logic Circuit    |      |

| 3    | VO      | Power Supply for Driving the LCD |      |

| 4    | RS      | Data/Instruction select          |      |

| 5    | R/W     | Read/Write select                |      |

| 6    | Е       | Enable signal                    |      |

| 7~14 | DB0~DB7 | Data Bus Line                    |      |

### 10.2 Block diagram